SID Display Week 2021 聴講記 (2) LTPO対抗技術

UDDI Technical Writer Ph.D. 鵜飼育弘氏の特別寄稿

SID2021聴講 (2) は、シンポジュームからLTPO (Low Temperature Polycrystalline Oxide) 対抗技術に関して日本の大学及び企業からの講演を取り上げる。先ずはLTPOとは?から始める。なお、図表の転載は許可を得ている。

LTPO技術とは?

Appleは、2018年発売のApple Watch Series 4にLTPOと名付けた最新のバックプレーンを搭載し注目を集めた。Apple Watch Series 4のLTPO OLED Displayは、SIDの2019 Display Industry Awardsを受賞し、技術者が講演も行った (1) 。ここでは、本題に入る前にホールド型駆動とTFTバックプレーンについて述べる。次にLTPO技術の特徴と課題を明確にする。

ホールド型駆動とTFTバックプレーン

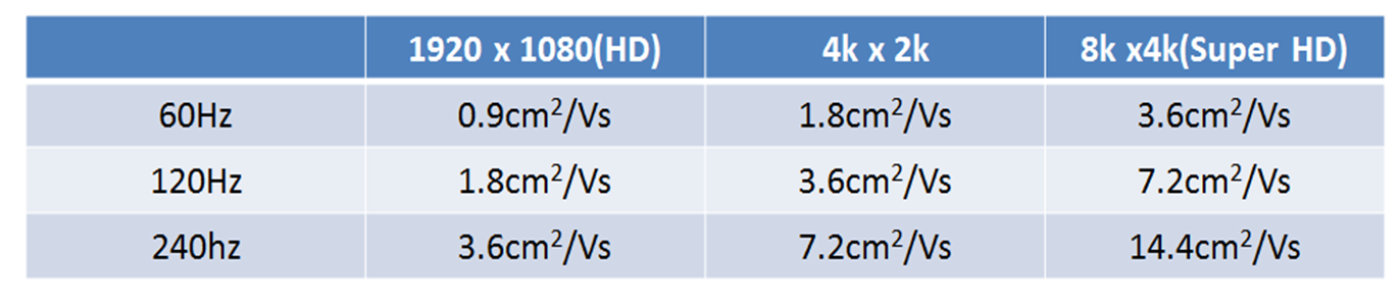

TFT-LCDやAMOLEDの駆動方式にはTFTをスイッチングデバイスに用いたホールド型が用いられている。フリッカーや動画ぼやけを防ぐには、フレーム周波数を60Hz以上にする必要がある。ディスプレイの表示容量およびフレーム周波数とTFTの移動度の関係を表1に示す。表から、例えばHDディスプレイを120Hzで駆動するにはTFTの移動度は1.8cm2/Vsを必要とすることがわかる。

表2にTFTの種類と特性および作製方法を示す表から、低温ポリシリコン (low temperature poly-Si: LTPS) は移動度が大きいのでOn電流 (VG>0) は一番大きいが、Off電流 (VG<0リーク電流) は、酸化物半導体であるIGZO (In-Ga-Sn-O) であるIGZOが一番小さい、ことがわかる。

LTPOの特徴と課題

Apple Watch 4に採用されたLTPOは、LTPSとIGZOの利点を組み合わせたTFTである。ディスプレイ上の各ピクセルには、LTPSとIGZOが同時配置されている。LTPOの特徴は、移動度が大きく安定性が高いLTPSを利用していること、そしてTFTの均一性が良く、リーク電流が少ないIGZOの利点を一つに結合した技術である。Apple Watchはモバイルデバイスであり、時刻を見るたびにスイッチをオンするようでは消費者には受け入れられない。そこで、如何に常時オン状態でデバイスの消費電力を低減できるかが重要である。

消費電力を下げる方法として、フレーム周波数を下げる方法があるが、表示画面の書き換えの周期が長くなり、リーク電流によってOLEDの輝度が低下する。フレーム周波数が60Hz以下になるとこの輝度変化が視認されるようになり、いわゆるフリッカーとして気になる。

Apple Watch 4に採用されたLTPOでは、1-60Hzの範囲でフリッカーがほとんど感じられないような制御を実現した。上述のようにIGZO-TFTは、オフ電流が非常に低く、リーク電流が桁違いに少ないため、次の書き換えまでの輝度変化が小さくできることによる。

またLTPOでは、ディスプレイ周辺回路や画素部のスイッチングにLTPS-TFTを用いている。上述のように、移動度が大きいことからスイッチング速度の高速化が可能というLTPSの特徴を活かせる。しかも、ディスプレイ周辺回路は、LTPSを用いることにより、バックプレーン上に一体形成することができる。これにより狭額縁化が可能で、表示面積を拡大することができる。

Apple Watch以外への応用としてスマートフォンが候補に挙がっている。しかし、如何にプロセスステップ数を減らし歩留まりを上げコストを下げるかがメーカーの勝負どころである。

対抗技術

SID2020シャープ (IGZO7)

Appleは、競争力のある武器として使用するために、最先端のディスプレイ技術を自社製品に投入し続けることが期待されている。しかし、ディスプレイメーカーはAppleの特許でディスプレイデバイスを製造する立場から脱却すべきである。

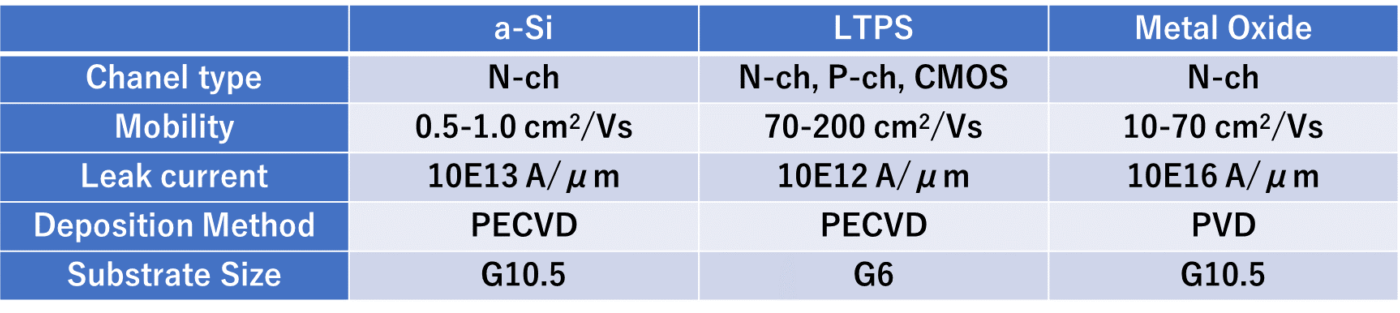

シャープはSID2020の講演で、LTPS-TFTと同等のIGZO7の開発に成功したと報告した (図1参照) (2)。IGZO7 TFTは、LTPOに比べ簡単なプロセスで低フレームレートと狭額縁のOLEDディスプレイを実現できることを示した。その結果、IGZO-TFTの1つの工場で、小型のスマートフォンから大面積のTVまで、さまざまなバックプレーンを作製できる。

SID2021に見る対抗技術

ここでは、次の2講演の概要を、論文を引用しながら述べる。

1. 固相結晶化による高移動度 IGO:H TFT

高知工科大学古田守教授から”High Mobility Hydrogenated Polycrystalline In–Ga–O (IGO:H) Thin-Film Transistors formed by Solid Phase Crystallization”と題した講演 (3)。

ポリIGO膜のキャリア密度は、10%未満のGa含有量を追加することで約1017cm-3に減らすことができる。水素化IGZO中の水素は、IGZO堆積時に意図的に水素を添加すると、金属水素 (MH) 結合を形成することにより、アニーリングによりキャリアサプレッサーとして機能することが報告されている。 IGO:H膜に意図的にドープされた水素は、膜堆積中の結晶化を抑制した。As-depoのアモルファスIGO:H膜は、250℃未満の低温固相結晶化SPC (solid phase crystallization) によってポリIGO:H膜に変換できる。 SPC-IGO:H膜のキャリア密度は、水素を含まないpoly-IGO膜のキャリア密度よりも2桁以上低くなる可能性がある。 50.6 cm2 / Vsの最大µFEは、SPC poly-IGO:HTFTから得られた。多結晶OSは、将来のディスプレイ用の高性能TFTを実現するためのシンプルで費用対効果の高いアプローチである。

SPC-IGO:H TFTの作製と特性評価

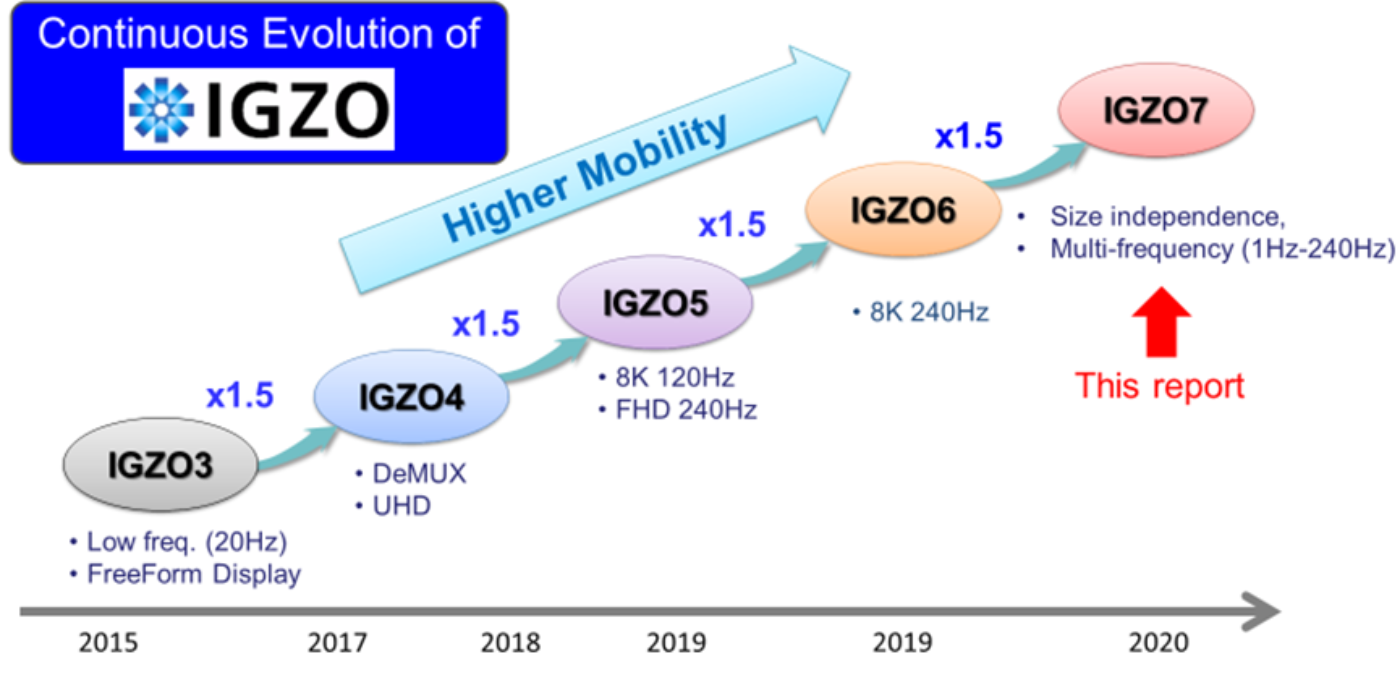

図2に、SPC-IGO:H TFTの作製プロセスとTFTの断面図を示す。poly-IGOとSPC-IGO:H TFTはSiO2 / Si基板上に作製した。ゲート絶縁体 (GI) として厚さ100 nmの熱酸化SiO2を用い、高濃度にドープされたSiウェーハをゲート電極として使用した。 GI表面のUV / O3洗浄後、30 nmの厚さのIGOおよびIGO:H膜を、基板を加熱せずにRFスパッタリングによって堆積した。 R (O2) は両方のフィルムで4%に設定した。

IGO膜はH2なしで堆積したが、IGO:H膜は3、5、および9%のR (H2) で堆積した。次に、両方のフィルムを空気中300℃で1時間アニールした。ソースおよびドレイン (S / D) 電極は、Al / Mo積層膜によって形成した。 IGOチャネルとS / D電極は、シャドウマスクによって形成した。厚さ100nmのSiO2パッシベーション層 (PVL) は、プラズマ化学気相成長法 (PE-CVD) により、180℃でテトラエトキシシラン (TEOS) とO2をソースガスとして使用して堆積した。最後に、電気測定の前に、TFTを20℃で1時間アニールした。 TFTのチャネル長と幅はそれぞれ1400と350µmである。

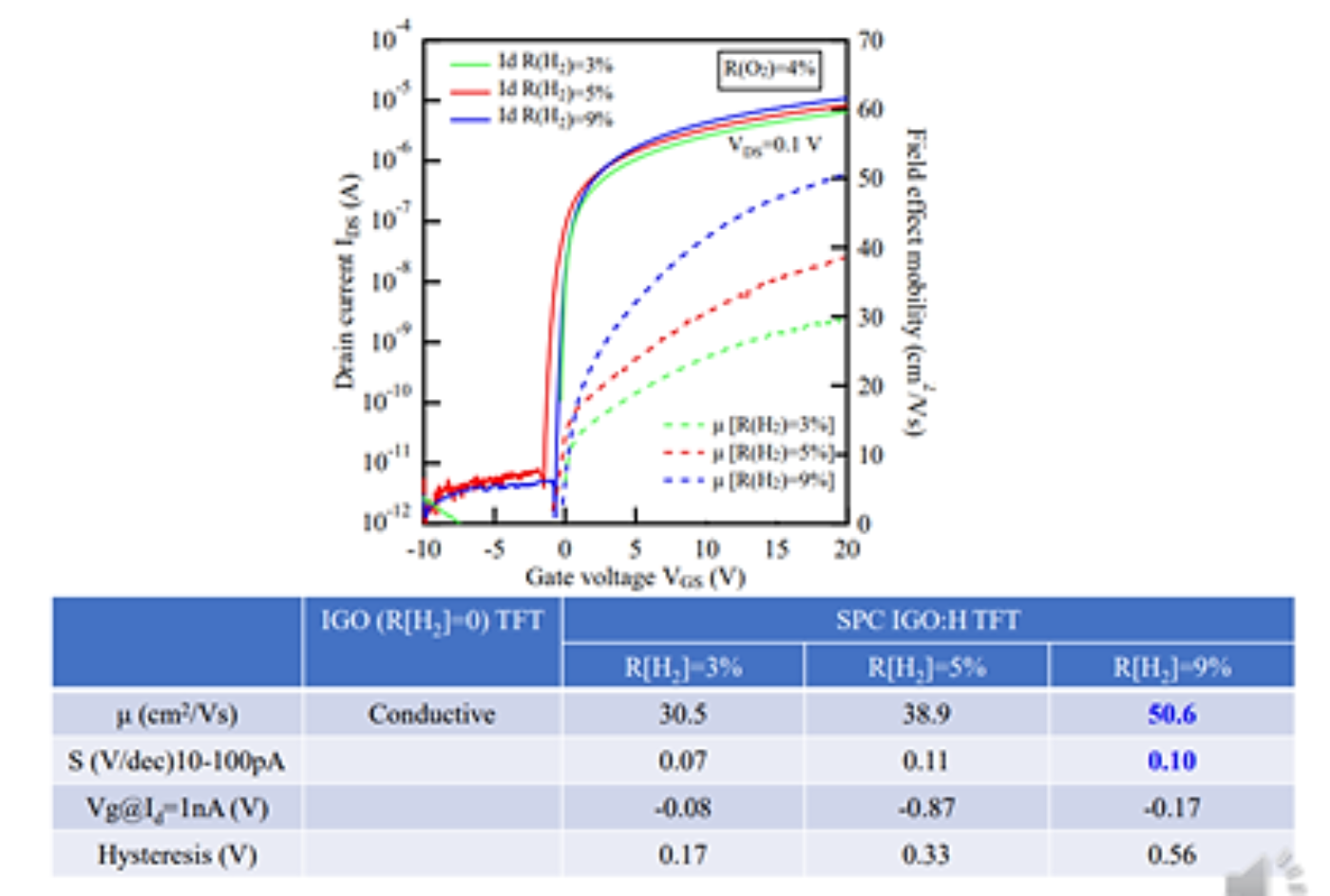

図3は、SPC-IGO:Hチャネルが3、5、および9%のR (H2) に成膜したTFTの転送特性を示す。Poly-IGO TFT (H2なしで堆積) は、上述ようにIGO膜のキャリア密度が高い (3.0×1019cm-3) ため、導電性の挙動を示した (データは図3に示していない) 。

対照的に、R (H2) に3、5、および9%のSPC-IGO:Hチャネルで作製したすべてのTFTは、0.07〜0.10 Vの範囲の急なサブスレッショルドスイング (SS) で良好な伝達特性を示した。しきい値電圧 (Vth) は、1 nAの正規化されたドレイン電流 (L / W×ID) を流すために必要なゲート電圧 (VG) によって定義した。

抽出したTFTの電気的パラメータを同図表にまとめた。IGO:Hチャネルの堆積中にR (H2) が増加すると、TFTのオン電流とµFEの両方が増加することがわかった。最大µFEは50.6 cm2 / Vs、S.S.値は0.10 V / decである。そして、-0.2 VのVth値は、9%のR (H2) でSPC-IGO:HTFTから得られた。

まとめ

要約すると、高移動度の多結晶IGO:H TFTは、低温固相結晶化によって実証した。 IGO:H膜堆積中のH2ドーピングは、膜堆積中の結晶化を抑制した。As-depoのアモルファスIGO:H膜は、250℃未満の低温SPCによってポリIGO:H膜に変換できる。 SPC-IGO:Hの粒子サイズは、as-depoのIGO:H膜の核密度の減少により、約270nmに拡大した。 SPC-IGO:H膜のキャリア密度は、水素を含まないpoly-IGO膜のキャリア密度よりも2桁以上低くなる可能性がある。 R (H2) に3、5、および9%のSPC-IGO:Hチャネルに堆積したTFTは、良好な伝達特性を示した。 TFTのオン電流とµFEの両方は、IGO:Hチャネルの堆積中にR (H2) が増加するにつれて増加した。 50.6 cm2 / Vsの最大µFEは、9%のR (H2) に堆積したSPC-IGO:Hチャネルを備えたTFTから得られた。多結晶OSは、将来のディスプレイ向けに高性能OSTFTを実現するためのシンプルで費用対効果の高いアプローチである。

著者所見

LTPSとOSによるLTPOTFTがAppleの製品に採用されたことで各社が量産を始めている。しかし、LTPOのTFT構造および製造プロセスは複雑である。その結果、LTPS-TFT製造の固有設備としてのイオン注入装置やエキシマレーザーアニール (ELA) 装置が必要である。この開発は、複雑なTFT構造やプロセスを用いないでLTPOと同等のTFT特性を実現したことは素晴らしい。

2. 青色レーザーダイオードアニーリングによるラテラル結晶Si

V-Technology鳥山誠也氏から” Fabrication of Lateral Crystal Si on Cu Bottom-Gate Structure via Blue-Laser Diode Annealing (BLDA)”と題した講演 (4)。

近年、G6以上のガラス基板サイズの拡大や、OLEDやμ-LEDなどの自発光素子の開発により、高いTFT移動度と均一性が求められている。しかし、ELAにはTFTの移動度や電気特性の不均一性に限界がある。また、ELAはランニングコストが高く、光学系としてG6以上のガラスサイズに対応することは困難である。

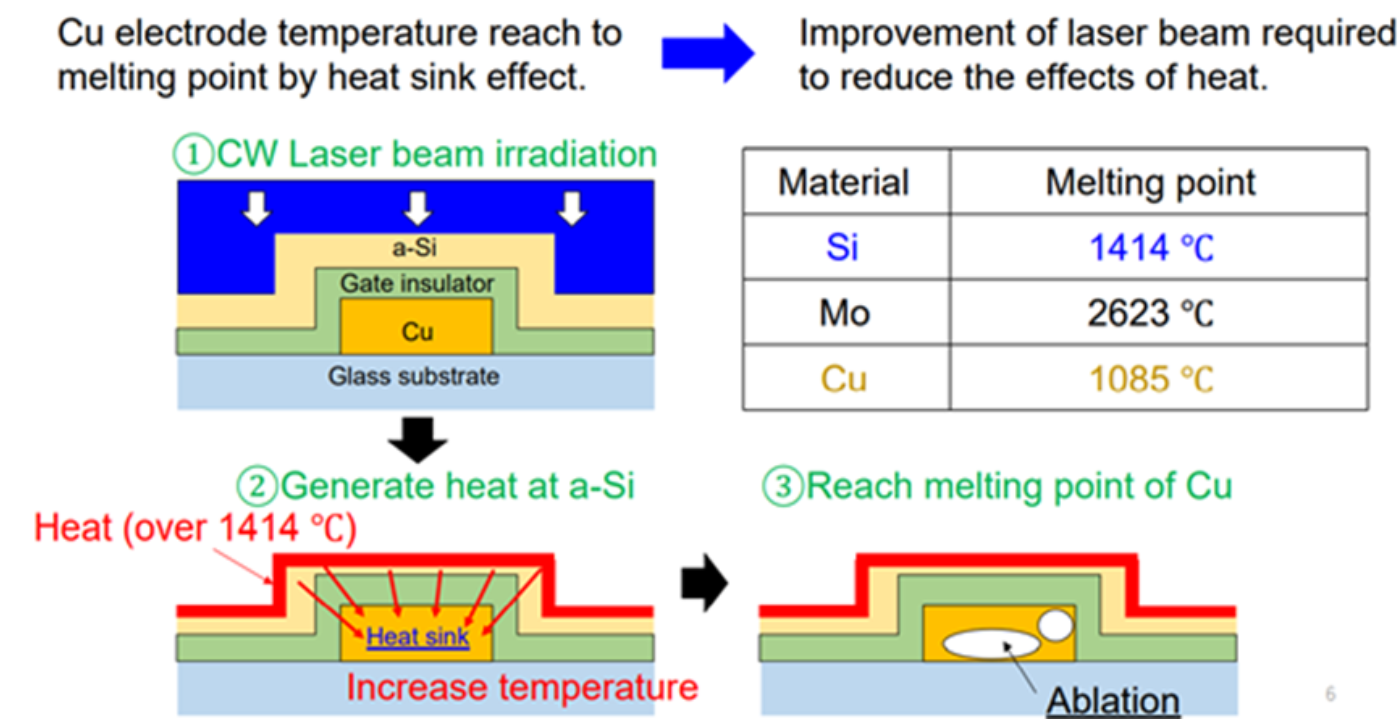

連続波 (CW : continuous wave) レーザーアニーリングは、ラテラル結晶や単結晶のように大きな粒子サイズの Si を製造することができる。このような大きな結晶は、TFT の移動度を大幅に向上させ、高い均一性を実現する。しかし、CWレーザーアニールには、アニール時の熱線が発生するという問題がある。 CWレーザーアニールはELAに比べ照射時間が長く、サーマルストラスによるゲート電極やガラス基板へのダメージの原因となる (図4参照)。

実験準備

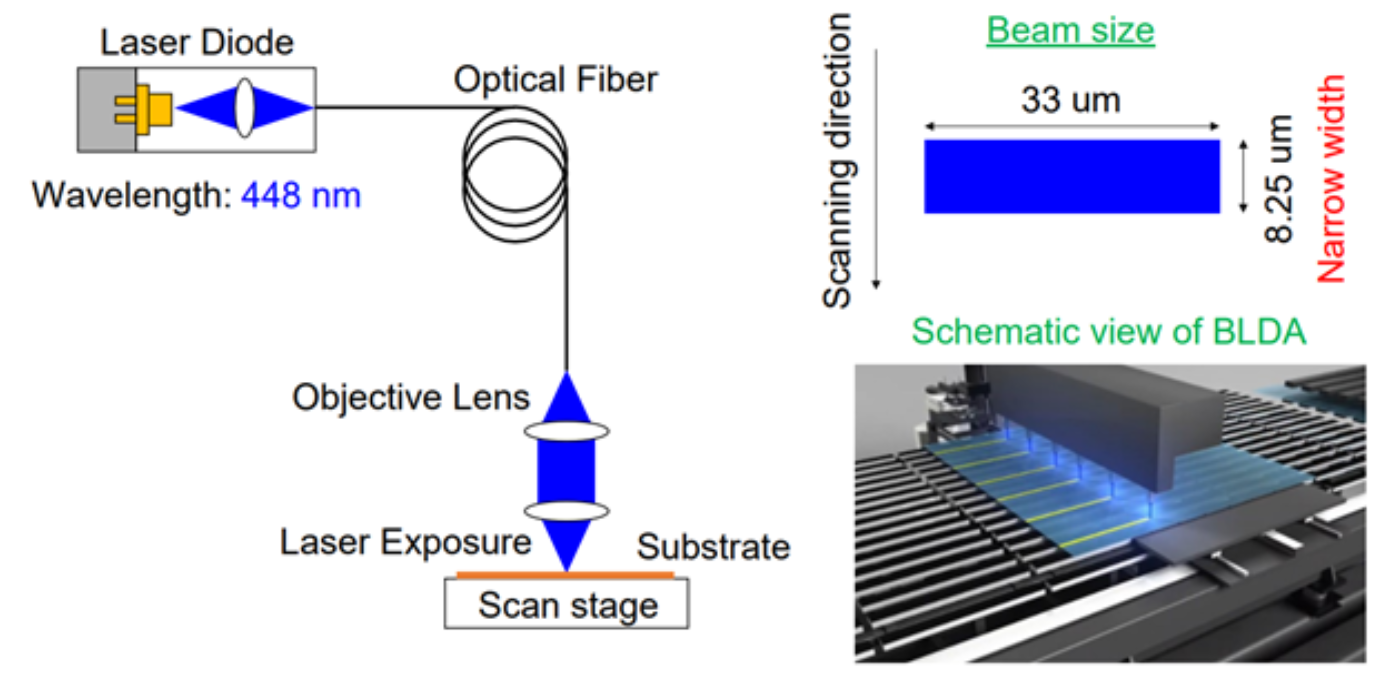

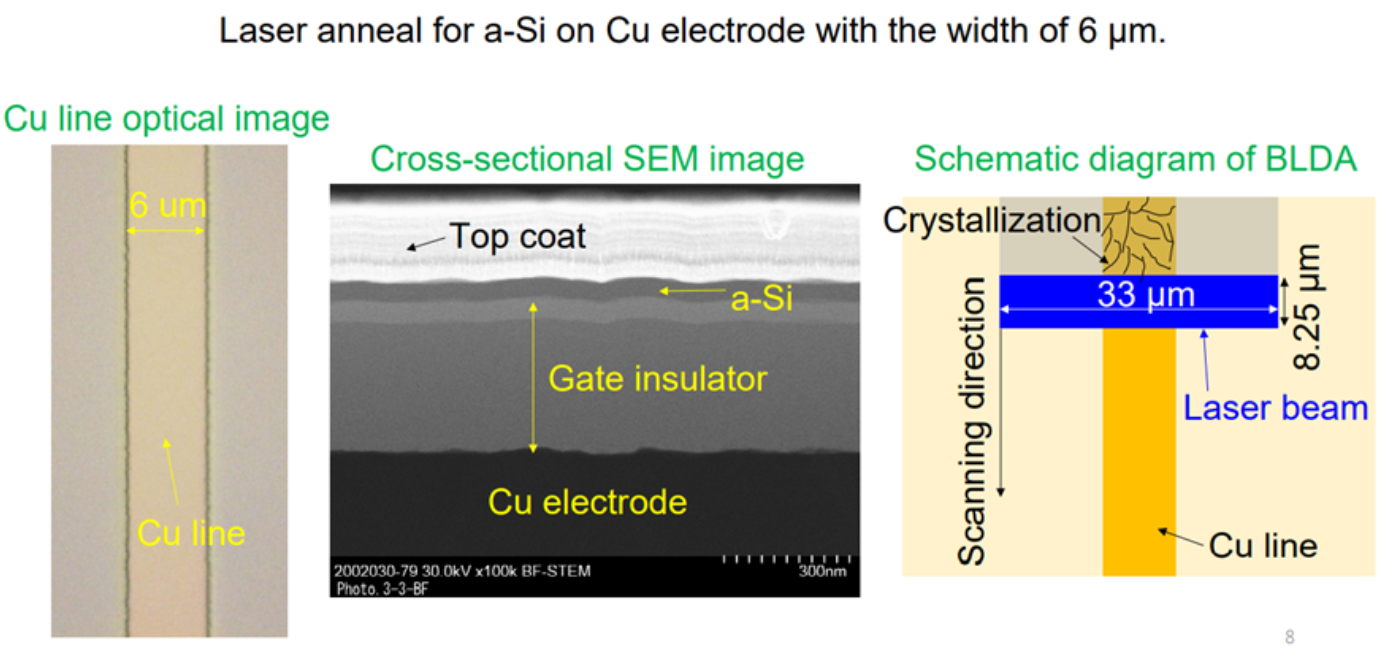

Cu電極のノンダメージレーザーアニールを実現するために、BLDA光学系を採用した。 図5は、当社の BLDA 光学セットアップ示す。 レーザー波長は448 nm、走査方向のレーザービーム幅は 8.25 μm、垂直方向は 33 μm を使用した。 光ファイバーを使用することでビーム形状は長方形である。 試料をステージ上に固定し、スキャンアニールを行った。 レーザービームは、Cu ボトムゲート構造上の a-Si に照射した。 サンプルのコンポーネントは、ガラス基板上に 50 nm の厚さの Cu 下部ゲート電極、ゲート絶縁体、および a-Si である (図6参照)。

Cu電極幅依存性

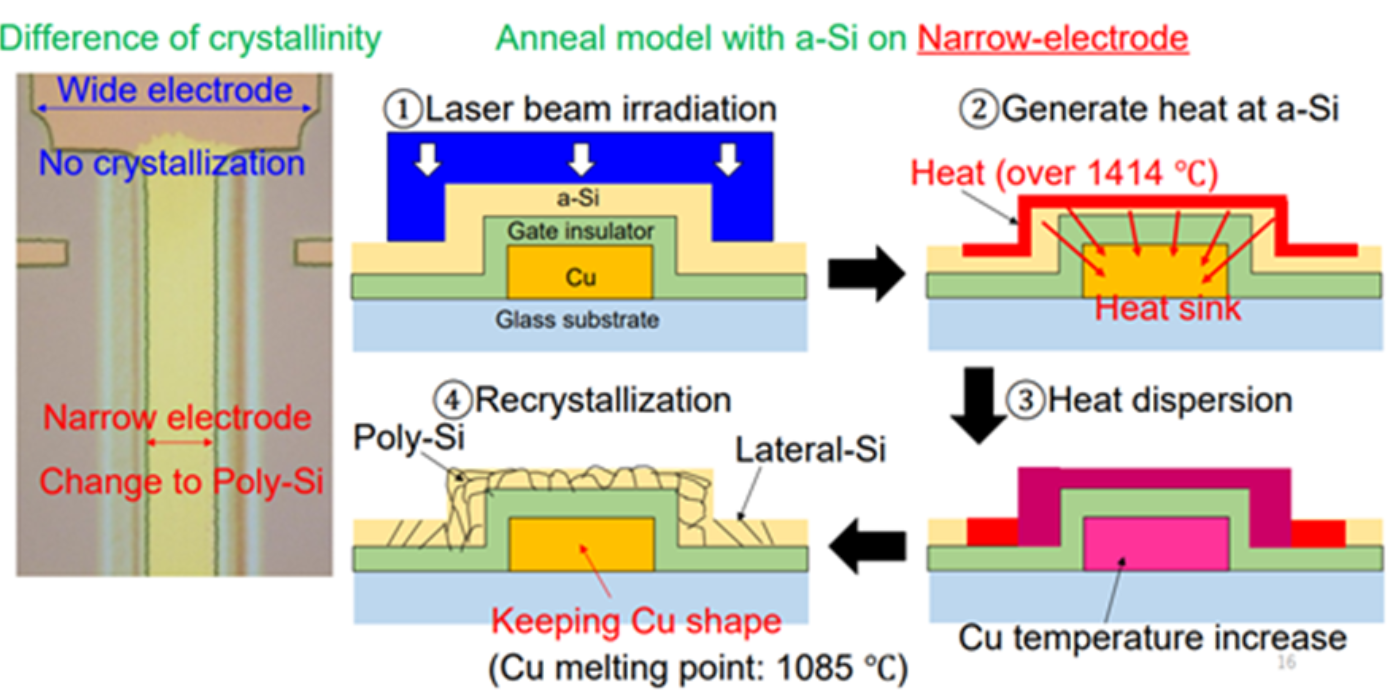

Cu電極幅と結晶化の差異を図7 (狭い電極幅の場合) と図8 (広い電極幅の場合) を示す。図7から、電極幅が狭いので銅の温度が上昇し、電極の形状を維持しながらラテラル成長がえられる。

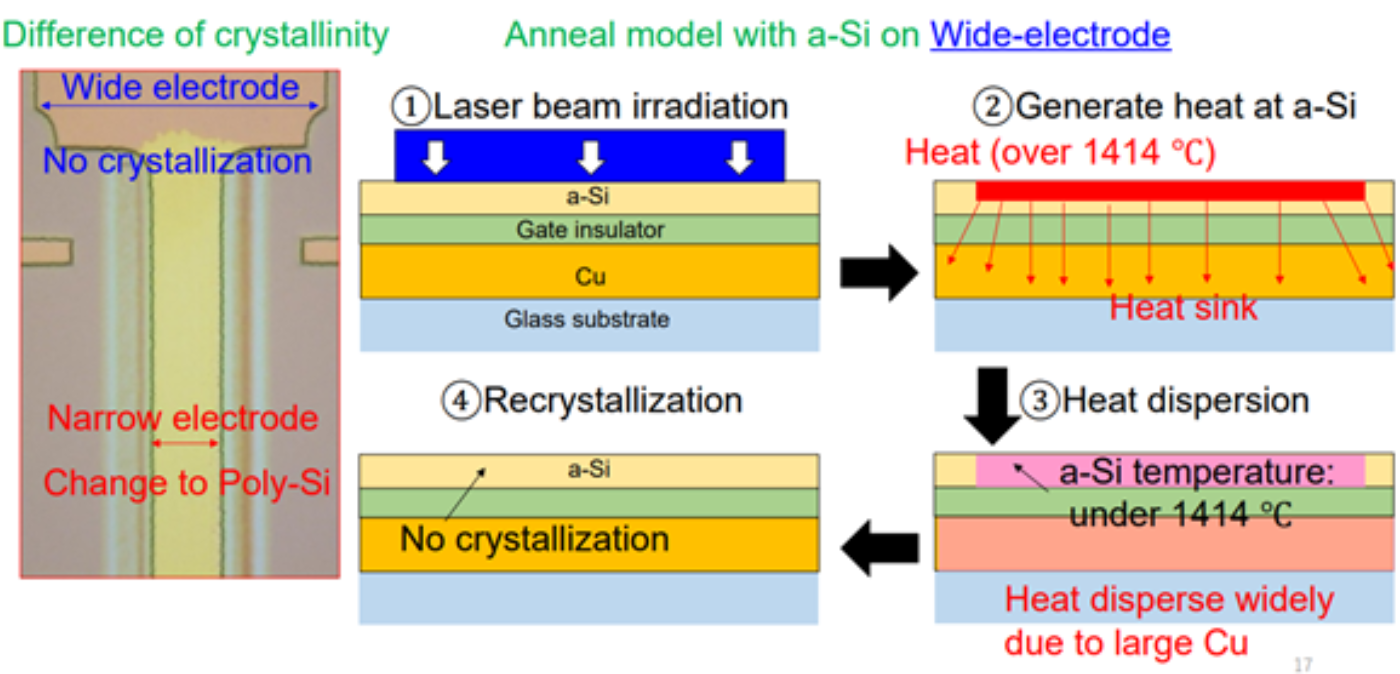

電極幅が広いと、熱が分散し結晶化は得られない。

当社の BLDA システムは、熱問題の解消を達成し、電極損傷のない Cu ボトム ゲート構造上に Si 横方向結晶が作製できることを確認した。 Siを効率よく溶融させるためのレーザー照射時間を短縮するために、青色の波長を採用し、ビームサイズを小さくし、走査速度を速くした。さらに、レーザーアニール時に発生する熱は、Cu電極の形状とサイズに依存することがわかった。ラテラル結晶は結晶欠陥が少ないため、ボトムゲート型のTFTは電気的特性が向上し、ばらつきが小さくなる。 BLDAシステムはELAに比べコストダウンが可能で、G10などの大型基板にも対応可能である。当社のBLDAシステムは、Mini LEDバックライトやOLEDへの適用が期待されている。

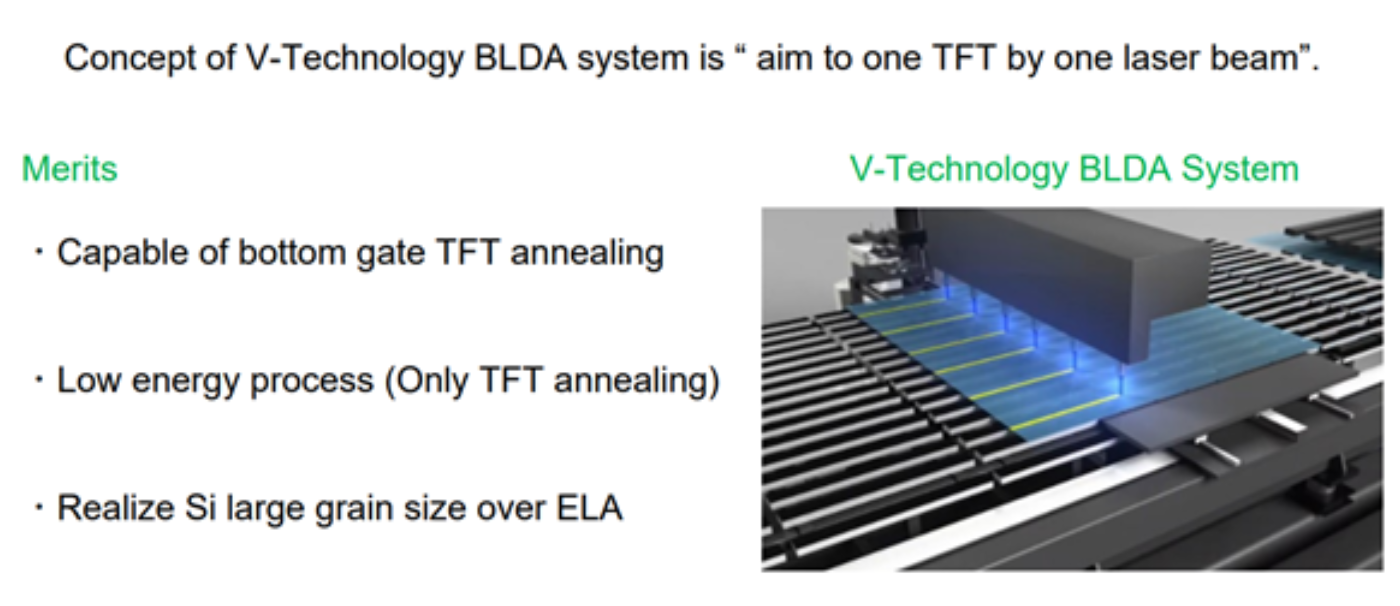

BLDA マルチスキャンシステム

開発したマルチビーム BLDA 光学系の模式図を図9に示す。 8.25μm×33μmの青色レーザービームを採用。 レーザービームはTFTピッチに合わせて配置される。 TFTのないところはレーザーアニールされない。 たとえば、Mini-LED バックライトの TFT ピッチは、LCD、OLED TFT よりも長くなる。 ELAのような太いラインビームは、TFT領域以外にもレーザーを照射するため、コストが高くなる。 BLDA マルチスキャンシステムは、ELA に比べて低コストの技術である。

まとめ

Cu電極上にラテラル結晶 Si を損傷なく作製することができた。 Cu 電極上の Si の断面画像は、電極に損傷がないことを示している。 電極の CW レーザーアニールでは、電極材料の熱伝導率が支配的であると推定される。

当社のBLDAシステムは、Mini LEDバックライトやOLEDへの応用が期待されている。

著者見解

ELAの課題は、著者が現役時代に身をもって体験した。装置コスト、ランニングコスト、稼働率、歩留まりへのインパクトなど多かった。勿論現在は、課題の多くは解消されているが、基板サイズの大型化とコスト削減は困難であろう。

V-Techが開発中の装置は、ハードにとどまらず、プロセス条件およびデバイスの試作まで社内でやり遂げられるところが強みである。FTの特性を含め、今後の展開を期待したい。

【参考・引用文献】

(1) J.Donelan, Information Display 4/19 pp.20-21(2019)

(2) K. Ito, et al., SID Digest pp.343-346(2020)

(3) M.Furuta, et al., SID Digest pp.69-72 (2021)

(4) S.Toriyama, et al., SID2021 Digest pp.96-98 (2021)

UDDI Technical Writer

Ph.D. 鵜飼育弘

yasuhiro.ukai@hotmail.co.jp

※ウェブサイト管理者より: 以下の「WRITTEN BY」表記は、システム上の都合により、DSCCウェブサイト編集者の情報となります。